芯片与硬件

2026-04-03

来源:TechCrunch

3 小时前

芯片革命新起点:台积电2纳米工艺启动风险试产,GAA晶体管时代正式来临

今天,全球半导体行业的目光再次聚焦于中国台湾新竹。台积电(TSMC)正式宣布,其备受瞩目的下一代2纳米制程(内部代号N2)已经迈入“风险试产”阶段。这不仅仅是一个技术节点的简单推进,它标志着晶体管技术一个新时代的开启,其背后采用的“纳米片晶体管”(GAAFET)架构,是自2011年FinFET(鳍式场效应晶体管)技术问世以来,芯片制造领域最根本的一次结构变革。根据台积电的规划,这项技术预计将在2026年底走向大规模量产,为未来的计算设备注入全新的动力。

**“风险试产”意味着什么?**

对于普通读者而言,“风险试产”这个词听起来可能有些令人不安。但在芯片制造业,这是一个非常积极且关键的里程碑。它意味着台积电已经完成了2纳米工艺的基础研发和初步验证,开始在其实验室或早期生产线上,使用实际的、复杂的设计(通常是来自其最重要客户的产品,比如苹果、英伟达或高通的下一代芯片原型)进行小批量试生产。

这个过程之所以“有风险”,是因为新工艺尚未完全成熟,良率(即合格芯片的比例)可能还很低,生产成本极高。但它的核心目的,正是通过与真实芯片设计的“磨合”,来发现并解决制造过程中最后、也是最棘手的工程问题。可以把它想象成一艘全新设计的巨轮,在正式投入跨洋航线前,进行的首次远海试航。台积电敢于宣布进入这一阶段,说明其2纳米技术的核心路径已经走通,技术可行性得到了验证,剩下的主要是优化和规模化的问题。

**从“Fin”到“片”:一场静默的架构革命**

要理解2纳米(N2)为何如此重要,我们需要先看看我们现在的芯片是怎么造出来的。过去十多年,从智能手机到数据中心服务器,几乎所有的高性能芯片都基于一种名为“FinFET”(鳍式场效应晶体管)的技术。你可以把它想象成在硅基底上竖起一片片微小的、鱼鳍状的硅墙,电流从这些“鳍”的三面流过,从而实现了比之前平面晶体管更好的栅极控制和更低的漏电。

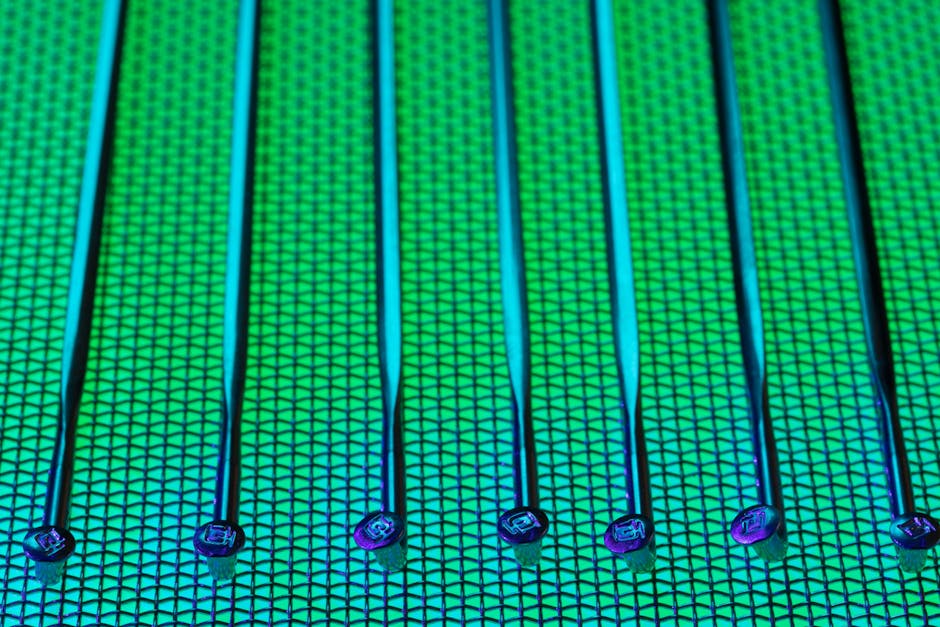

然而,随着晶体管尺寸不断微缩,FinFET也遇到了物理极限。当“鳍”的宽度逼近几个原子层时,控制电流的难度呈指数级上升,漏电和功耗问题变得难以忍受。于是,业界早已将目光投向了下一代技术:GAAFET,全称是环绕式栅极晶体管。而台积电N2工艺采用的“纳米片晶体管”(Nanosheet FET),是目前GAAFET技术中最主流、也最成熟的实现方案。

与立体的“鳍”不同,纳米片晶体管的结构更像一个多层三明治。它通过堆叠多个极薄的硅片(即“纳米片”),让栅极材料从上下左右四个方向完全包裹住每一条电流通道。这种全方位的控制,就像用更精细的手套去握持一个物体,比只从三面握持(FinFET)要稳固得多。其直接好处是:在相同的供电电压下,晶体管的开关速度可以更快(性能提升);或者在提供相同性能时,所需的电压可以更低(功耗下降)。台积电官方曾透露,与目前的3纳米(N3E)工艺相比,2纳米(N2)在相同功耗下性能可提升10-15%,或在相同性能下功耗可降低25-30%。

**不止于手机:重塑计算的未来格局**

每当提到先进制程,人们的第一反应往往是“下一代iPhone的芯片会更强大”。这没错,移动设备永远是先进工艺最前沿的尝鲜者。但2纳米的意义远不止于此。它真正要服务的,是正在深刻变革全球的几股核心算力浪潮。

首先是**人工智能**。无论是云端训练万亿参数的大模型,还是在终端设备上进行实时推理,AI对算力和能效的需求是贪得无厌的。2纳米工艺带来的性能功耗提升,将直接转化为AI芯片(如GPU、TPU及各类ASIC)更强的计算密度和更低的运行成本。这可能会加速更大参数模型的诞生,以及让更复杂的AI应用在手机、汽车等边缘设备上成为可能。

其次是**高性能计算与数据中心**。气候变化和能源成本让数据中心的功耗成为全球性议题。2纳米技术有望在保持算力增长的同时,显著降低服务器的能耗,这对于谷歌、亚马逊、微软等云服务巨头以及各国超算中心来说,具有巨大的经济和社会价值。

最后是**自动驾驶与智能汽车**。一辆L4级以上的自动驾驶汽车,其车载计算平台的数据处理能力堪比一个小型数据中心,且必须在严苛的功耗和散热限制下工作。2纳米芯片将是实现更安全、更复杂自动驾驶系统的关键硬件基石。

**台积电的“护城河”与全球竞争**

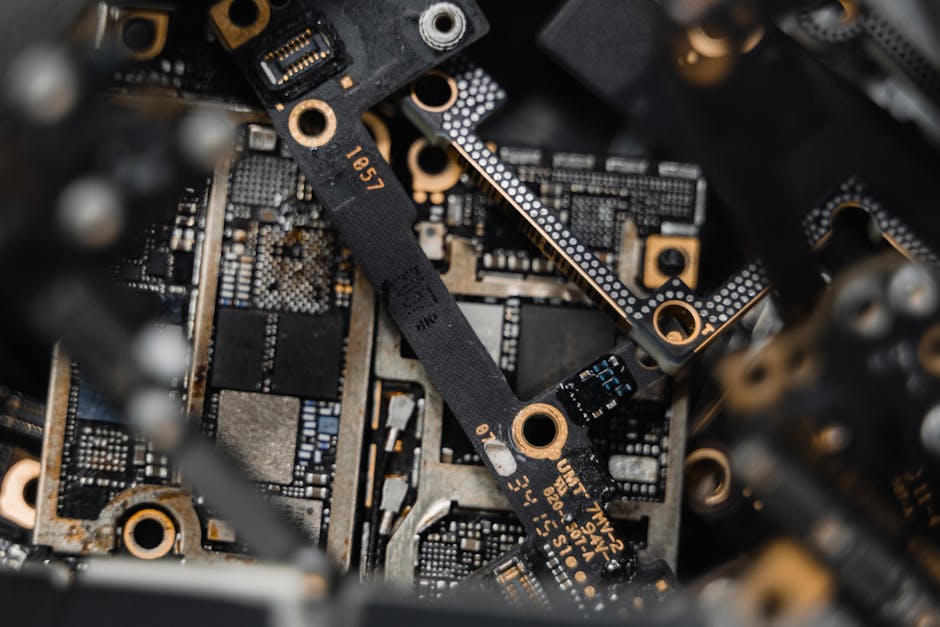

台积电此次宣布2纳米风险试产,不仅是一个技术公告,更是一次强有力的市场宣言。在全球半导体制造竞赛中,台积电、三星和英特尔正进行着一场“三国杀”。三星早已宣布其3纳米工艺采用了GAA技术(尽管其量产规模和良率面临挑战),并规划了2纳米的路线图。英特尔则在其“四年五个制程节点”的激进计划中,将20A(约相当于2纳米)和18A(更先进的2纳米级)作为重夺技术领导地位的关键,并已宣布其18A工艺获得了重要客户。

台积电此时亮出清晰的N2时间表(风险试产进行中,2025年量产,2026年底大规模量产),旨在向全球客户,尤其是那些在AI时代押注未来的巨头们,传递一个明确的信号:在通往2纳米及更未来的道路上,台积电的技术路线依然稳健、可靠且领先。其庞大的客户生态、经过验证的制造经验和持续的资本投入,构成了它难以被短期逾越的“护城河”。对于苹果、英伟达、AMD、高通等公司而言,选择哪个代工厂的哪个节点,将直接决定其未来两到三年产品的竞争力。台积电的这一步,无疑是在巩固其作为“首选代工厂”的地位。

**结语:摩尔定律的下一站**

2纳米风险试产的启动,再次证明了摩尔定律——尽管步履维艰——仍在工程师们的智慧推动下前行。它不再仅仅是关于尺寸的缩小,更是关于材料、架构和封装技术的协同创新。从FinFET到GAAFET的跃迁,是芯片行业一个时代的交接棒。

当我们站在2024年展望2026年,台积电的2纳米芯片将不仅仅是手机里更快的处理器。它们将成为驱动AI突破、加速科学发现、实现全自动驾驶、并让数字世界与物理世界更深度融合的隐形引擎。这场始于纳米片晶体管的微观革命,其涟漪终将波及我们数字生活的每一个角落。风险试产,只是这场宏大叙事的最新一页。